Cortex-A7 基础

简介

Cortex-A7 MPCore

1-4core

Cortex-A15(big)+Cortex-A7(LITTLE)

L1 Cache 8,16,32,64KB

L2 Choice

Cortex-A7 MPCore 基于 ARMv7-A

- SIMDv2 扩展整形和浮点向量

- VFPv4 高性能单双精度浮点指令

- LPAE 40bit寻址 最大1TB内存

- 硬件虚拟化

- NEON 多媒体、信号处理加速

运行模式

Cortex-A7处理器有 9种处理模式,除了 User(USR)用户模式以外,其它 8 种运行模式都是特权模式。

| 模式 | 描述 |

|---|---|

| User(USR) | 用户模式,非特权大部分程序运行的时候就处于此。 |

| FIQ | 快速中断模式,进入 FIQ 中断异常 |

| IRQ | 一般中断模式。 |

| Supervisor(SVC) | 超级管理员模式,特权模式,供操作系统使用。 |

| Monitor(MON) | 这个模式用于安全扩展模式。 |

| Abort(ABT) | 数据访问终止模式,用于虚拟存储以及存储保护。 |

| Hyp(HYP) | 用于虚拟化扩展。 |

| Undef(UND) | 未定义指令终止模式。 |

| System(SYS) | 系统模式,用于运行特权级的操作系统任务 |

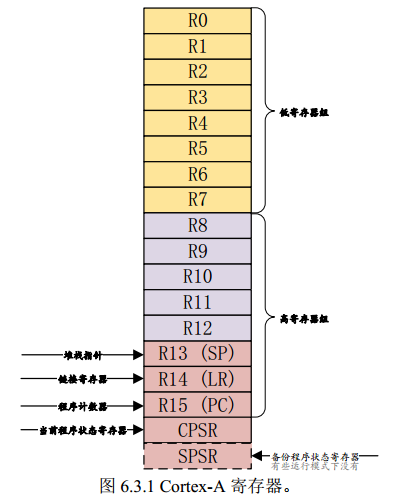

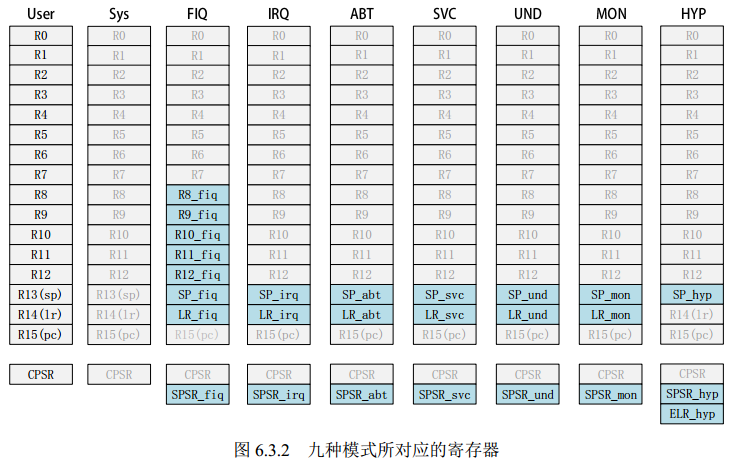

寄存器

- 暗色代表没有物理寄存器

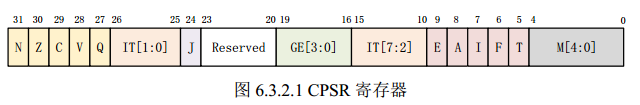

CPSR

CPSR 是当前程序状态寄存器,该寄存器包含了条件标志位、中断禁止位、当前处理器模式标志

等一些状态位以及一些控制位。

SPSR(备份程序状态寄存器) 备份CPSR的

N(bit31):当两个补码表示的 有符号整数运算的时候, N=1 表示运算对的结果为负数, N=0表示结果为正数。

Z(bit30): Z=1 表示运算结果为零, Z=0 表示运算结果不为零,对于 CMP 指令, Z=1 表示进行比较的两个数大小相等。

C(bit29):在加法指令中,当结果产生了进位,则 C=1,表示无符号数运算发生上溢,其它情况下 C=0。在减法指令中,当运算中发生借位,则 C=0,表示无符号数运算发生下溢,其它情况下 C=1。对于包含移位操作的非加/减法运算指令, C 中包含最后一次溢出的位的数值,对于其它非加/减运算指令, C 位的值通常不受影响。

V(bit28): 对于加/减法运算指令,当操作数和运算结果表示为二进制的补码表示的带符号数时, V=1 表示符号位溢出,通常其他位不影响 V 位。

Q(bit27): 仅 ARM v5TE_J 架构支持,表示饱和状态, Q=1 表示累积饱和, Q=0 表示累积不饱和。

IT[1:0].(bit26:25): 和 IT[7:2].(bit15:bit10)一起组成 IT[7:0],作为 IF-THEN 指令执行状态。

J(bit24): 仅 ARM_v5TE-J 架构支持, J=1 表示处于 Jazelle 状态,此位通常和 T(bit5)位一起表示当前所使用的指令集:

| J | T | bref |

|---|---|---|

| 0 | 0 | ARM |

| 0 | 1 | Thumb |

| 1 | 1 | ThumbEE |

| 1 | 0 | Jazelle |

GE[3:0].(bit19:16): SIMD 指令有效,大于或等于。

IT[7:2].(bit15:10): 参考 IT[1:0]。

E(bit9): 大小端控制位, E=1 表示大端模式, E=0 表示小端模式。

A(bit8): 禁止异步中断位, A=1 表示禁止异步中断。

I(bit7): I=1 禁止 IRQ, I=0 使能 IRQ。

F(bit6): F=1 禁止 FIQ, F=0 使能 FIQ。

T(bit5): 控制指令执行状态,表明本指令是 ARM 指令还是 Thumb 指令,通常和 J(bit24)一起表明指令类型,参考 J(bit24)位。

M[4:0]: 处理器模式控制位:

M[4:0] CPU Mode 10000 User 模式 10001 FIQ 模式 10010 IRQ 模式 10011 Supervisor(SVC)模式 10110 Monitor(MON)模式 10111 Abort(ABT)模式 11010 Hyp(HYP)模式 11011 Undef(UND)模式 11111 System(SYS)模式